# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to <a href="http://www.renesas.com/inquiry">http://www.renesas.com/inquiry</a>.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# M61558FP

# Power driver IC for 30-W × 1-channel digital amplifiers

REJ03F0060-0100Z Rev.1.0 Sep.19.2003

## **Description**

The M61558FP is a power driver IC for digital power amplifiers. The IC incorporates both pre-drivers and the outputstage n-channel power MOS FET, for a single chip implementation of a 30-W single-channel digital amplifier for audio applications.

#### **Features**

- On-chip n-channel power MOS FET

- Fast PWM switching operation

- On-chip diode for boot strap

- Various on-chip protective circuits

- VDD under detection circuit

- Over-Temperature protection circuit

- Over-current protection circuit

## **Recommended Operating Conditions**

Power-supply voltage for pre-drive stage: VDD = 12 V (pre-driver stage power-supply voltage)

Output-stage power-supply voltage: VD = 21 V (typ.) < 16 V (min.) to 24 V (max.), RL = 4 (min.), 6 (typ.), 8 (max.)  $\Omega$

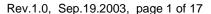

# System block diagram

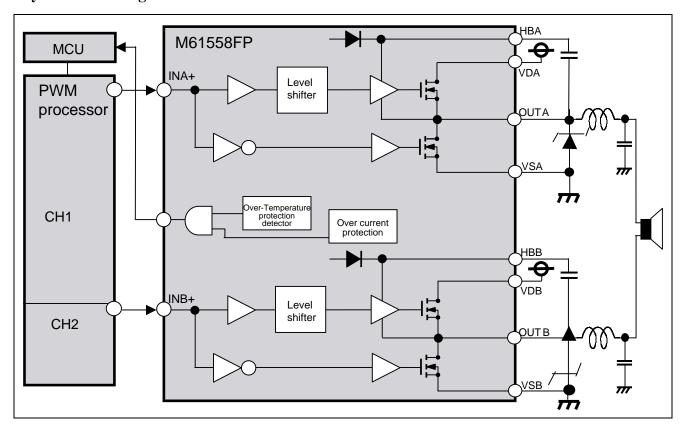

## Sample application circuit and pin assignments

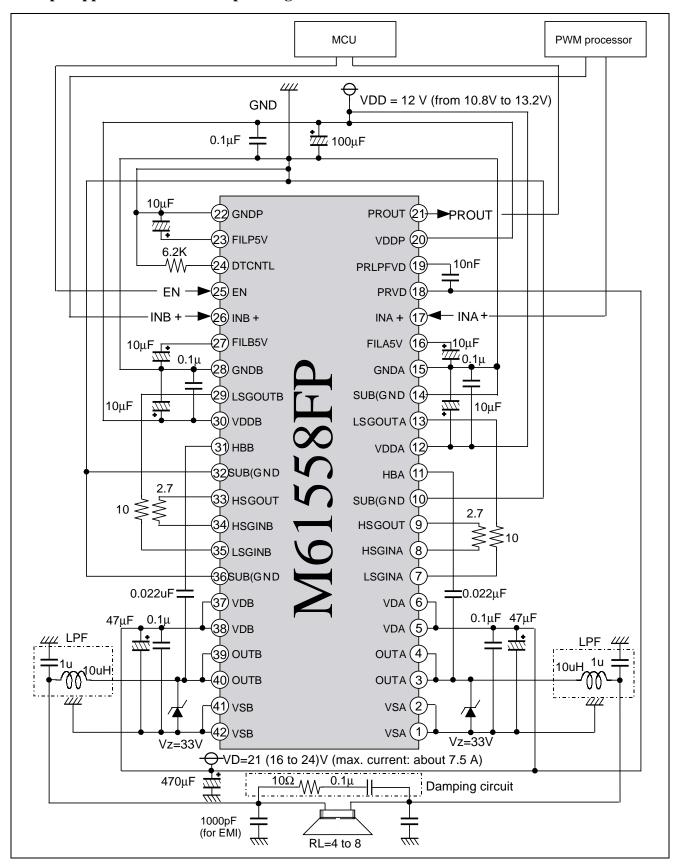

# **Block diagram**

# **Pin Descriptions**

|                 | Pin<br>No. | Pin Name      | Bin Description                                                                          |

|-----------------|------------|---------------|------------------------------------------------------------------------------------------|

| A-side          | 1, 2       | VSA           | Pin Description  Ground pin for the A-side power-output stage                            |

| power           |            | OUTA          |                                                                                          |

| module          | 3, 4       |               | A-side power-output pin                                                                  |

|                 | 5, 6       | VDA<br>LSGINA | Power-supply pin for A-side power-output stage                                           |

|                 | 7          |               | MOS FET input pin for A-side (L)                                                         |

| ۸ منام          | 8          | HSGINA        | MOS FET input pin for A side (H)                                                         |

| A-side          | 9          | HSGOUTA       | A side (H) pre-buffer output                                                             |

| pre-<br>control | 10         | NC            | Connected to ground                                                                      |

| module          | 11         | HBA           | A pin for A side (H) boot strap.*                                                        |

| modulo          | 12         | VDDA          | A-side pre-driver power-supply pin                                                       |

|                 | 13         | LSGOUTA       | A-side (L) pre-buffer output                                                             |

|                 | 14         | NC            | Connected to ground                                                                      |

|                 | 15         | GNDA          | A-side pre-driver ground pin                                                             |

|                 | 16         | FILA5V        | Filter pin for A-side 5-V internal generation power-supply                               |

|                 | 17         | INA+          | A-side PWM + input pin (CMOS input)                                                      |

| A, B            | 18         | PRVD          | Power-supply pin for over current protection. Connected to VD power supply.              |

| common          | 19         | PRLPFVD       | Filter pin for over-current protection circuit                                           |

| protec-         | 20         | VDDP          | Power-supply pin for protection circuit block                                            |

| tion<br>module  | 21         | PROUT         | Protection detector output pin. When protection condition is detected, low level (if pin |

| module          |            |               | is pulled up) is output (open drain output).                                             |

|                 | 22         | GNDP          | Ground pin for protection circuit block                                                  |

|                 | 23         | FILP5V        | Filter pin for generation of 5-V internal power-supply for protection circuits           |

|                 | 24         | DTCNTL        | For connection to a resistor for dead-time control                                       |

|                 | 25         | EN            | Enable pin that release from the protection state                                        |

| B-side          | 26         | INB+          | B-side PWM + input pin (CMOS input)                                                      |

| pre-            | 27         | FILB5V        | B-side 5-V internal generation power-supply filter pin                                   |

| control         | 28         | GNDB          | B-side pre-driver ground pin                                                             |

| module          | 29         | LSGOUTB       | B-side (L) pre-buffer output                                                             |

|                 | 30         | VDDB          | B pre-driver power-supply pin                                                            |

|                 | 31         | HBB           | Apm for B-side (H) boot-strap capacitor circuit.                                         |

|                 | 32         | NC            | Connected to ground                                                                      |

|                 | 33         | HSGOUTB       | B-side (H) pre-buffer output                                                             |

| B-side          | 34         | HSGINB        | B side (H) MOS FET input pin                                                             |

| power           | 35         | LSGINB        | B side (L) MOS FET input pin                                                             |

| module          | 36         | NC            | Connected to ground                                                                      |

|                 | 37, 38     | VDB           | B-side power-output stage power-supply pin                                               |

|                 | 39, 40     | OUTB          | B-side power-output pin                                                                  |

|                 | 41, 42     | VSB           | B-side power-output stage ground pin                                                     |

|                 | 71,74      | V O D         | 2 order permer output orage ground pin                                                   |

Note: \* Adjacent power-module pins that have the same names must be connected with the shortest possible wiring lengths.

## **Absolute Maximum Ratings**

| Parameter                       | Symbol   | Ratings     | Unit  | Conditions                                 |

|---------------------------------|----------|-------------|-------|--------------------------------------------|

| HBA, HBB max. operating voltage | HBA, HBB | 39          | V     | HBA, HBB pin voltage (operational setting) |

| VDA, VDB max. operating voltage | VDA, VDB | 25          | V     | VDA, VDB pin voltage (operational setting) |

| Absolute max. voltage rating    | VDD      | 15          | V     | VDD power-supply voltage                   |

| Voltage applied to input pins   | Vin      | -0.3 to 5.5 | V     |                                            |

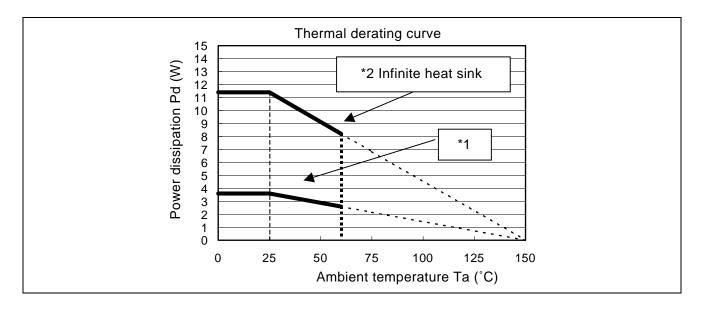

| Allowable dissipation           | Pd       | 3.6         | W     | Ta = 25°C (when mounted on the board       |

|                                 |          |             |       | specified by Renesas; see note 1)          |

| Thermal derating                | Κθ       | 28.8        | mW/°C | When mounted on the board specified by     |

|                                 |          |             |       | Renesas; see note 1)                       |

| Junction temperature            | Tj       | 150         | °C    |                                            |

| Operating temperature           | Та       | -20 to +60  | °C    |                                            |

| Storage temperature             | Tstg     | -40 to +125 | °C    |                                            |

Notes: 1. The specifications of the board specified by Renesas are given below for reference.

2. Maximum allowable power dissipation Pd = 11.4 W (ambient temperature Ta =  $25^{\circ}\text{C}$ ) with an ideal heat sink.

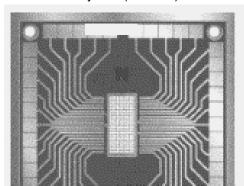

Layer 1 (surface)

Layer 2 (rear)

\*1 Thermal derating characteristics measured for the board specified by Renesas

(Board specifications)

Material: Glass epoxy FR-4 Dimensions: 70 × 70 mm Thickness: t = 1.6 mm

(Wiring specifications for layers 1 and 2)

Material: Copper Thickness: t = 18 mm

#### **Precautions on Usage**

- 1. This product radiates heat even during normal operation, and reaches high temperatures. There is a possibility that characteristics failure or breakdown, including in peripheral components and circuits, may cause this product or peripherals to reach abnormally high temperatures. Also, please take special care when using this product as the final stage, since it may then be susceptible to damage because of external factors. This product is designed for consumer applications. Accordingly, please use it within the specified thermal conditions. Usage of the product in more relaxed thermal conditions may lead to malfunctions or damage to the product.

- 2. This product incorporates an over-current protection circuit which terminates the PWM operation when the peak instantaneous current from the VDA or the VDB power supply exceeds 7.5 A (designed value). Please note that it is never required to supply more current than this.

- The maximum-current value is roughly below 3 A during operation with a standard 4-  $\!\Omega$  load.

- In usage, care is required with regard to the stability of the power-supply voltage.

3. Detection of an abnormality (when the PROUT pin (pin 21) becomes low) indicates a po

- 3. Detection of an abnormality (when the PROUT pin (pin 21) becomes low) indicates a possibility of over current, so eliminate the cause, such as shorting of the output pins, and release the IC from the protection state (input low level on the EN pin (pin 25)).

- 4. This product includes MOS FET and CMOS logic circuits. Accordingly, electrostatic break down or latch-up may be generated within these elements. Please take the same care in using this product as in any case where MOS FET and CMOS logic LSIs are in use.

## **Recommended Operating Condition**

|                            |         | Limits | ;    |      | _    |                                           |

|----------------------------|---------|--------|------|------|------|-------------------------------------------|

| Item                       | Symbol  | Min.   | Тур. | Max. | Unit | Condition                                 |

| VD power-supply voltage    | VD      | 16     | 21   | 24   | V    | VDA (pins 5, 6), VDB (pins 37, 38)        |

| VDD power-supply voltage   | VDD     | 10.8   | 12.0 | 13.2 | V    | VDDA (pin 12), VDDB (pin 30), VDDP        |

|                            |         |        |      |      |      | (pin 20)                                  |

| PWM frequency              | fpwm    |        | 0.7  | 1.5  | MHz  | INA+ (pin 17), INB+ (pin 26)              |

| Min. operating pulse width | Tpw MIN | 40     | _    | _    | ns   | INA+ (pin 17), INB+ (pin 26)              |

| High input voltage         | VinH    | 4.0    | _    | 5.0  | V    | INA+ (pin 17), INB+ (pin 26)              |

| Low input voltage          | VinL    | 0.0    | _    | 0.8  | V    | INA+ (pin 17), INB+ (pin 26), EN (pin 25) |

#### Notes:

### 1. PWM operation

Do not input a signal shorter than the minimum pulse width, since this may lead to unstable operation or, in the worst case, damage to the product. Since boot-strap operation is performed, an input signal with aperiodical high and low levels may lead to abnormal operation. Ensure that the PWM signal has periodical high and low levels. The capacitance of the capacitor for boot-strapping in the sample application diagram is for the product in operation at 768 kHz. The thermal conditions, etc., become looser with operation at lower PWM frequencies.

#### 2. Power-supply voltage

The normal operating condition for this product is VDD voltage < VD voltage, so ensure that this is the state during normal operation. Setting a lower VDD voltage increases the margin against damage but carries the danger of the under voltage detection circuit malfunctioning, so please ensure that VDD is maintained at 9 V or more.

#### 3. Mounting (board)

The board layout must be capable of handling the same high frequencies and high levels of power as are handled by this IC. Furthermore, components must be selected in consideration of both audio-frequency and high-frequency characteristics. Please external note that large surges are generated by parasitic inductances during high-speed switching. This IC is designed specifically for bridge-tied load (BTL) operation, so the design focus was on symmetry of sides A and B. The pattern on the board must also be highly symmetrical for BTL configuration.

RENESAS

## **Electrical characteristics**

(Unless otherwise noted, Ta = 25°C, VDDP, VDDA, B = 12 V, VDA, B = 21 V)

|                                               |               | Limits     |       |      | _    |                                              |  |

|-----------------------------------------------|---------------|------------|-------|------|------|----------------------------------------------|--|

| Item                                          | Symbol        | Min.       | Тур.  | Max. | Unit | Condition of measurement                     |  |

| Current drawn by the circuit                  |               |            |       |      |      |                                              |  |

| VDD current circuit                           | IDDQS         | _          | 15    | _    | mA   | PWM-suspended state                          |  |

| (suspended)                                   |               |            |       |      |      | ·                                            |  |

| VDD current circuit                           | IDDQ          | _          | 35    | _    | mA   | No signal (f = 768 kHz, duty cycle = 50%)    |  |

| VD current circuit                            |               | _          | 40    | _    | mA   | No signal (f = 768 kHz, duty cycle = 50%)    |  |

| Signal interfaces                             |               |            |       |      |      |                                              |  |

| High input signal                             | VIH           | 2.3        | _     | _    | V    | Pins INA+, INB+, EN                          |  |

| Low input signal                              | VIL           | _          | _     | 1.0  | V    | Pins INA+, INB+, EN                          |  |

| High level input current                      | IIH           | -10        |       | 10   | μΑ   | Pin EN                                       |  |

| Low level input current                       | IIL           | -260       | -130  | -65  | μΑ   | Pin EN                                       |  |

| Low output voltage                            | VOL           |            |       | 0.4  | V    | Pin PROUT: IOL = 1 mA                        |  |

| High-output (leakage) current                 | IOH           |            | _     | 10   | μΑ   | Pin PROUT: VOH = 5 V                         |  |

| 3                                             |               |            |       |      |      |                                              |  |

| Protection detectors                          |               |            |       |      |      |                                              |  |

| VDD under voltage detection                   | VDDR          | 5.0        | 7.0   | 9.0  | V    | Between VDD and GND, drop-                   |  |

| level                                         |               |            |       |      |      | detected to normal                           |  |

| Hysteresis in VDD-detection voltage           | VDDH          |            | 0.5   | —    | V    | Normal to under voltage                      |  |

| Over Temperature protection start temperature | Tsd+          |            | 150   |      | °C   | Normal to over-temperature protection state* |  |

| Over Temperature protection end temperature   | Tsd-          |            | 130   |      | °C   | Over-temperature to normal state*            |  |

| Diode characteristics for boot-s              | strap         |            |       |      |      |                                              |  |

| Diode forward-direction voltage               | VFL           |            | 0.75  | _    | V    | HB output current = 100 μA                   |  |

| Diode forward-direction voltage               | VFH           |            | 1.0   | _    | V    | HB output current = 100 mA                   |  |

| Diode dynamic resistance                      | RDON          | _          | 0.7   |      | Ω    | HB output current = 100 mA                   |  |

| Gate driver for low-side power                | transistor: " | on" voltac | je    |      |      |                                              |  |

| Low level output voltage                      | VOL           | _          | 0.5   | _    | V    | ILO = 100 mA                                 |  |

| High level output voltage                     | VOH           | _          | -0.75 | _    | V    | IHO = -100 mA                                |  |

| 0                                             |               |            |       |      |      |                                              |  |

| Gate driver for high-side powe                | r transistor: | "on" volta | ge    |      |      |                                              |  |

| Low level output voltage                      | VOL           | _          | 0.5   | _    | V    | ILO = 100 mA                                 |  |

| High level output voltage                     | VOH           |            | -0.75 | _    | V    | IHO = -100 mA                                |  |

| <del>-</del>                                  |               | _          |       |      |      |                                              |  |

<sup>\*:</sup> Note that Tsd+, Tsd- are designed values for the IC's internal temperature.

(Unless otherwise noted,  $Ta = 25^{\circ}C$ , VDDP and VDDA/B = 12 V, VDA/B = 21 V)

|                                            |             | Limits |      |      |      |                               |

|--------------------------------------------|-------------|--------|------|------|------|-------------------------------|

| Item                                       | Symbol      | Min.   | Тур. | Max. | Unit | Condition of measurement      |

| Output-stage DMOS transistor               | ON resistan | ce     |      |      |      |                               |

| Breakdown voltage between drain and source | BVds        | 35     | _    | _    | V    | lleak=1mA                     |

| ON resistance between drain and source     | rDS(ON)     | _      | 0.20 | _    | Ω    | ID=100mA                      |

| Input/output timing                        |             |        |      |      |      |                               |

| Reference input operating frequency        | 1/tpf       | _      | 768  | _    | KHz  | Boot-strap C = 0.022 uF       |

| Min. input pulse width                     | tpw         | 40     | _    | _    | ns   | Period = 1.3 us (f = 768 kHz) |

| Dead-time setting                          |             |        |      |      |      |                               |

| Pin 24 output voltage                      | VDTC        | _      | 1.35 |      | V    | Connected resistance: 6.2 kΩ  |

#### (Data for reference) AC characteristics

Note: The reference values when the evaluation board specified by Renesas is used.

(Unless otherwise specified, Ta = 25°C, VDDP and VDDA/B = 12 V, VDA/B = 21 V)

|                                 |        | Rated | ed value Re |      | Reference board set |                                             |                                                      |

|---------------------------------|--------|-------|-------------|------|---------------------|---------------------------------------------|------------------------------------------------------|

| Item                            | Symbol | Min.  | Тур.        | Max. | Unit                | condition                                   | Measurement condition                                |

| Output<br>power 1               | Po1    | _     | 30          | _    | W                   | Sine, 1 kHz/0 dB,<br>modulation depth = 90% | THD+N=1%,RL=6Ω,<br>VDA/B=24V                         |

|                                 |        |       |             |      |                     |                                             | LPF=20KHz,<br>HPF=400Hz                              |

| Output<br>power 2               | Po2    | _     | 30          | _    | W                   | Sine, 1 kHz/0 dB,<br>modulation depth = 90% | THD+N=1%,RL=4Ω,<br>VDA/B=21V<br>LPF=20KHz, HPF=400Hz |

| Total<br>harmonic<br>distortion | THD+N  | _     | 0.04        | _    | %                   | Sine, 1 kHz/0 dB,<br>modulation depth = 50% | RL=4Ω,<br>LPF=20KHz,<br>HPF=400Hz                    |

| Noise<br>voltage                | Vno    | _     | 150         | _    | μVrms               | The MUTE signal is inputed                  | A-Weighted filter/<br>LPF=20KHz                      |

| Power efficiency                | Eff    | _     | 85          | _    | %                   | Sine, 1 kHz/0 dB,<br>modulation depth = 90% | Po=30W, RL=4Ω                                        |

Note: In the heat-radiation state of attachment to the board specified by Renesas, the M61558FP can continuously output 10 W (refer to the thermal derating curve on page 5). When more than 10 W is continuously output, heat-radiation design measures such as heat sinks are required.

## **Description of additional functions**

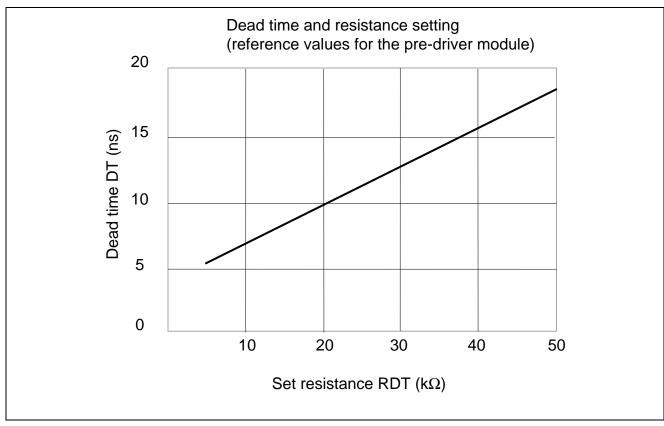

#### **Dead-time control**

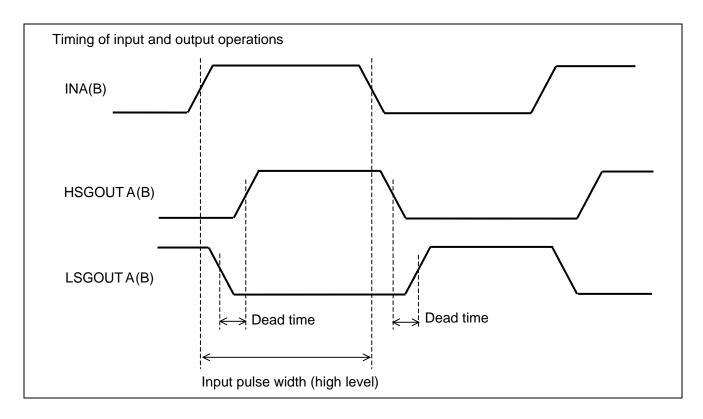

The dead-time value given below sets a period between LSGOUTA(B) and HSGOUTA(B) at the gate-driver outputs. This prevents through-current-induced damage to the output-stage power transistor. The dead-time setting is adjusted by the value of the external resistor on DTCNTL (pin 24).

Note: The given values are design values, and the actual dead time is affected by the operating conditions (gate-resistor value, switching characteristics, etc.) of the power transistor.

#### Internal protective circuits

1. VDD under voltage detection circuit

When the VDD power-supply voltage falls by a certain amount, the VDD under voltage protective circuit operates to prevent malfunctions of the IC. When an abnormality is detected, the output transistor on the H side is switched off, the output transistor on the L side is switched on, and a low level is output from the output pin. For the sake of automatic resumption, a low level is not output from PROUT (pin 21). Of the protection states, this is only the case for abnormal voltage-drop detection. The VDD detection circuit is connected to the common VDD power-supply pin, VDDP (pin 20). Please set up IC-external wiring to connect the VDDA/B (pins 12, 30) to VDDP.

2. Over Temperature protection circuit

The IC incorporates an over temperature protection circuit (thermal shutdown circuit) that protects the IC from thermal damage when the temperature of the IC (chip) rises because of an abnormality. The protection circuit is activated before the IC's internal junctions, etc., reach the thermal-damage temperature, and remains so until the temperature falls to the hysteresis condition, regardless of the state of the EN pin (pin 25). In the excessive-temperature condition, all output transistors are turned off, the output pins are released (open), and a low level is output from PROUT to issue a notification about the abnormal state.

3. Over current protection circuit

This IC incorporates an excessive current protection circuit which terminates the PWM operation when the peak instantaneous value of current supplied from the VDA or VDB power supply exceeds 7.5 A (designed value). In the protection mode, all output transistors are switched off, all output pins are released (open), and a low level is output from PROUT to notify the system of the abnormal state.

Note: The abnormality is detected on the positive side of the power-stage power supply. The conditions for detecting a load short between output pin and VDD. VDD are not more strict short between both output pins or between output pin and ground. Note that when shorting between VDD occurs, detection is not possible until the abnormality affects the positive side of the power supply, so the protective operation may not be performed.

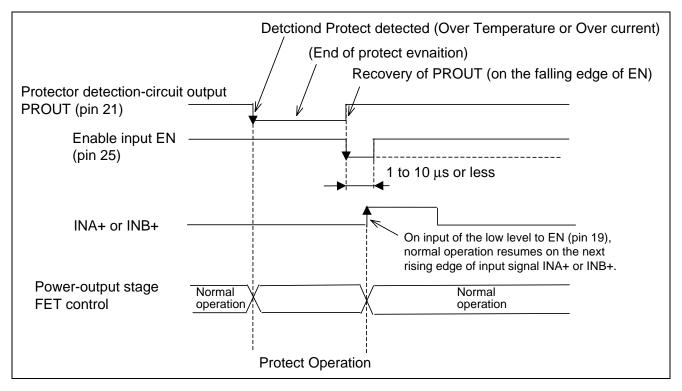

#### Functions when an abnormality is detected

When an abnormality is detected, the IC operates asynchronously with respect to the PWM inputs (INA+, INB+), controls the output-stage n-channel transistor (H or L side) and enters the protection state. The states of the PROUT and OUT outputs and the states of each output-stage transistor are given in the table below. After the low level has been placed on PROUT, the protection state is maintained until the EN signal is low.

State of output stage during protection operation

|                                           | PROUT output in case of                          | OUTA       | OUTB       | OUTA o | utput-<br>ansistor | OUTB o<br>stage tra | •      |

|-------------------------------------------|--------------------------------------------------|------------|------------|--------|--------------------|---------------------|--------|

| Protection                                | abnormality                                      | output pin | output pin | H side | L side             | H side              | L side |

| VDD voltage-drop protection               | No change (high)                                 | Low        | Low        | Off    | On                 | Off                 | On     |

| Over Temperature, over-current protection | Output low, held until low level is placed on EN | Open       | Open       | Off    | Off                | Off                 | Off    |

#### Resuming from abnormality detection

Resumption to signal output from the individual abnormal state varies with the corresponding protective circuit. After the conditions for resumption have been satisfied, resumption occurs on the rising edge of either INA+ or INB+, whichever is earlier. The conditions for resumption from each abnormal state are given in the table below.

### Conditions required for resumption from abnormal states

| Abnormal state                 | Condition for resumption                                                                                                                                                                              |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD under voltage              | After the voltage has returned to the normal level and this has been confirmed by the internal VDD detection circuit, the IC resumes normal operation on the next rising edge of either INA+ or INB+. |

| Over Temperature, over current | After the state has returned to normal, the condition for resumption is the falling edge of EN. The IC then returns to normal operation on the next rising edge of either INA+ or INB+.               |

## Timing chart for protector detection-output PROUT (pin 21) and enable input EN (pin 25)

#### LPF circuit

The output LPF circuit must have characteristics in accord with the signal-frequency band and characteristic impedance value of the speaker that constitutes the load. The simplest example is a second-order Butterworth filter in an LC configuration.

#### **Damping circuit**

When the speaker is removed, the frequency characteristics of the low-pass filter may lead to problems of high-band characteristics such as peaking. Accordingly, a high-band damping circuit should be installed in parallel with the speaker. (Take the allowable power, etc., of the damping resistor into consideration.)

#### Zener diode for surge protection

Ringing, etc., occurs during the high-speed switching operation of this IC. During short-circuit, connection to ground or VDD of load, very large surge voltages are generated. When the surge voltage exceeds the voltage tolerance of the transistors (step-down voltage between source and drain, etc.), the IC may be damaged. We recommend that you prevent damage to this IC by connecting a Zener diode for surge protection to the output pins (select a Zener voltage slightly below 35 V).

#### Precautions on wiring for the protective circuits

PRVD (pin 18) is wired to the protective detection circuits.

Use as short a wiring run as is possible to connect this pin to a point on the VD power-supply line near the VD pin. This point should not be readily affected by variation in voltages due to power supply and the operating conditions.

Please take care because this may affect the characteristics of the protective circuits or damage the IC.

#### Measures against EMI

Please note the need to reduce the levels of unwanted radiation components produced by high-speed switching operation. For example, apply countermeasures such as raising the order of the output LPF circuit, or attaching a capacitor with a value of about 1000 pF to the speaker pin.

#### Single-ended operation

This IC is for bridge-tied load (BTL) operation, but single-ended operation for an independent half-bridge configuration is possible. In this case, note that performance changes (e.g. 30 W x 1 ch. becomes 7.5 W x 2 ch). Also, other parts of the IC are designed on the specific assumption of BTL operation, so sufficient evaluation and examination is required.

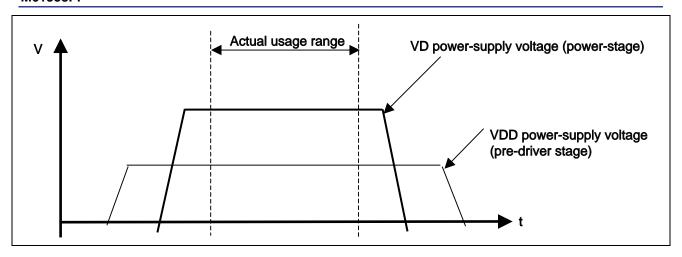

#### Pop noise when turning the power supply on and off

One simple countermeasure against pop noise is to ensure that VD (power-stage power-supply voltage) is only turned on and off while VDD (power-supply voltage of the pre-driver stage) is applied. If this measure is ignored, pop noise may occur when the power supply is turned on or off.

We also recommend operation under the condition VDD < VD. Consider turning the power supply on and off in the following sequence.

#### **Heat sink**

Unlike the molded resin surface, the metal side of the package for heat radiation is slightly concave. Take this structure into consideration when designing a heat sink for use with high output levels.

#### Capacitor for boot-strapping

This IC is designed for PWM operation at around 768 kHz (high-speed PWM operation in the hundreds of kHz order). Accordingly, the value of the capacitor for boot-strapping in the diagram of the example application circuit is for such operation. If a large change is to be made to the PWM frequency, a correspondingly change in the value of this capacitor is required. Note that such usage was not presupposed in the design of this IC.

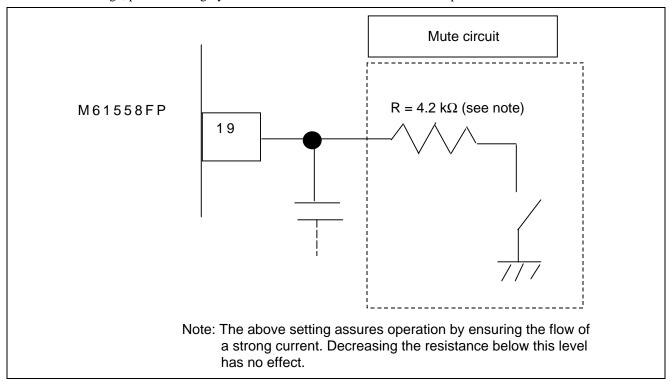

#### Muting operation by force

The output is forcibly muted by using a resistor to pull the PRLPFVD pin (pin 19) down to ground (signal output is terminated and the output terminals enter the Hi-Z open state; refer to the figure below). To cancel muting, release pin 19 from the pulled-down state, and then input a cancellation pulse on the EN pin (pin 25) in the same way as is used to cancel the protection state.

Please note the following points:

- Muted operation is only possible during normal operation; that is, it is not possible in transient states, such as while turning the power supply on or off.

- For actual usage, please thoroughly evaluate and examine the forcible mute operation.

# M61558FP

# **Package Dimensions**

42P9R-E

Note: Please contact Renesas Technology Corporation for further details.

Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Keep safety first in your circuit designs!

The pastery in a survival circula designs; and the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss resident product product of the responsibility of the information of the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances i

- use.

6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

**RENESAS SALES OFFICES**

http://www.renesas.com

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500 Fax: <1> (408) 382-7501

Renesas Technology Europe Limited.

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, United Kingdom Tel: <44> (1628) 585 100, Fax: <44> (1628) 585 900

Renesas Technology Europe GmbH Dornacher Str. 3, D-85622 Feldkirchen, Germany Tel: <49> (89) 380 70 0, Fax: <49> (89) 929 30 11

Renesas Technology Hong Kong Ltd. 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2375-6836

Renesas Technology Taiwan Co., Ltd. FL 10, #99, Fu-Hsing N. Rd., Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology (Shanghai) Co., Ltd. 26/F., Ruijin Building, No.205 Maoming Road (S), Shanghai 200020, China Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952

Renesas Technology Singapore Pte. Ltd.

1, Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

| _ |  |  |

|---|--|--|